# INTEGRATION OF A CHEMICALLY-AMPLIFIED PHOTORESIST AND A PANEL AND WAFER-LEVEL PACKAGING STEPPER FOR ADVANCED PACKAGING TECHNOLOGIES

Jack Mach Rudolph Technologies Wilmington, MA 02155 USA Ph: 978-253-6200 Email: jack.mach@rudolphtech.com

Joe Lachowski, Rosemary Bell Dow Electronic Materials Marlborough, Massachusetts, U.S.A.

#### Abstract

Advanced packaging technologies require materials that will allow for better resolution of patterns associated with the ever more challenging device architecture, along with materials that will allow for higher throughput. Device throughput can be increased with imaging materials that have higher sensitivity. Chemically-amplified photoresists offer the advantages of excellent sensitivity and resolution with good process margins, coupled with excellent stripping performance and plating bath compatibility for the film thicknesses that are required in packaging applications. However, it is the integration of the photomasking material and the availability of today's advanced back-end exposure tools that allow for improved lithographic imaging. It is this combination that is necessary for meeting the demands of today's higher resolution and tighter pitch requirements for back-end plating applications, which is essential in producing metallized structures for copper pillar and solder applications. Because the profile of the resist image is directly transferred during the electroplating process, it is critical to have a well-formed image that is resistant to the plating chemistry. Plating bath contamination and resist strippability are other key factors in producing void-free, defect-free structures.

Dow's newly-introduced chemically-amplified material is capable of film thicknesses from 30µm to 80µm by a single coating process with good uniformity. Imaging and process latitude at multiple wavelengths using a 0.1NA WLP/PLP stepper and a 0.15NA PLP stepper are demonstrated at 50µm thicknesses with emphasis on sidewall profiles and sensitivity. The power of integrating enhanced image contrast via chemical amplification and improved optical design has enabled the development of higher resolution, finer pitch backend processing for advanced packaging technologies.

#### Key words

Chemically Amplified Resist (CAR), High Aspect Ratio Cu Pillar, High Density, Panel-level, Wafer-level Stepper

### I. Introduction

Advanced packaging technologies have experienced rapid advancement in recent years. Advanced packaging processes are the realm in which multiple chips within a single package are interconnected, providing added functionality and increased performance while at the same time condensing it into the smaller volumes required for integration into today's consumer electronics. Advanced packaging uses a number of approaches (i.e. 2D, 2.5D and 3D). This paper will concentrate on 2.5D approaches in wafer- and panel-level chip scale packaging. Of particular interest is the replacement of solder bumps by fine pitch copper pillar bumps, the subject of many new SiP designs.

# **II. Experimental Details**

## A. Methodology

From a strictly spatial standpoint, the density of copper pillars is limited by a combination of the critical dimension (CD) and the sidewall profile of the vias in resist. With vertical sidewalls, no footing or topping, pillar density would be near infinite, plating challenges aside. With any tapering of the sidewall, topping or footing, for a given CD, the maximum achievable density will be limited as it can result in parts of the pillars being too close together when plated. With a small enough via and large enough foot, it's possible that a large bulk of the plated pillars are undercut and lift right off due to instability. Too much of an undercut in the resist mold while targeting a footed pillar would results in the resist bulk lifting off.

#### B. Reticle Layout

The testing method required bespoke reticles to be designed and manufactured for each of the lithography systems used in this exercise. The reticle design includes arrays of different sized vias at various pitches. Plating considerations were also taken into account during the design phase.

#### C. Photoresist

Dow's INTERVIA<sup>TM</sup> BCPR-i 4500 Photoresist was selected for the purposes of this study. This photoresist is a chemically amplified positive material designed specifically for advanced packaging applications. Chemically amplified systems offer the advantages of excellent sensitivity and resolution with good process margins on broadband and iline exposure tools. This material was formulated specifically for compatibility with a number of plating chemistries and is easily removed after plating. These attributes, coupled with a usable film thickness range of 30-80μm, make this an ideal photoimageable layer for pillar formation of varying heights and pitch ratio.

Copper-seeded wafers were spin coated with the photoresist to a film thickness of 50µm and softbaked for five minutes at 135°C prior to exposure for all iterations and steps during testing. After exposure, a post-exposure bake was applied for three minutes at 90°C before the substrates were developed on a track system using four 60 second puddles of MF-26A, a 2.38% TMAH developer.

## D.Lithography Systems

When processing a thick photoresist, well controlled sidewall angles are a critical requirement, especially when electroplating tall copper pillars. Most front-end tools have high numerical aperture (NA) lenses with low depth of focus (DOF) that prevent adequate penetration of thick films with sufficient image contrast to achieve the side wall angle and resolution requirements. Mask aligners struggle with high aspect ratio imaging, not because of their NA, but because they are unable to provide the necessary focus offset required to penetrate the film at high resolution, limiting their ultimate aspect ratio and side wall angle control. Accurate focus control across the wafer or substrate is required to achieve consistent and accurate CD control with straight and perpendicular side walls.

The lithography steppers utilized in this study were the Rudolph Technologies JetStep $^{\textcircled{B}}$  W2300 System and JetStep $^{\textcircled{B}}$  G45HR.

The JetStep W2300 uses a 2x reduction 0.1 NA singletelecentric lens system that provides a very large DOF to maintain image integrity and CD control through thick films, a priority for high aspect ratio imaging when films exceed  $30\mu$ m. The stepper lens is achromatized and the installed "filter wheel" provides the user a choice of illumination wavelengths to expose the photoresist layers. Specifically, the user has the ability to image at either "broadband" ghi-(350-450nm), gh- (390 to 450nm) or i-line (365nm) wavelengths.

The JetStep G45HR is a Gen 4.5 panel system that uses a 0.15 NA 1.25x magnification double-telecentric lens system that provides a 200mm field to maintain high throughput while delivering smaller CDs. This is an i-line (365nm) optics system that allows for magnification and trap to be handled independently of focus.

Both systems utilize "on the fly" focus control systems to ensure that every exposure is at the optimum focal plane height. This capability is essential when advanced packaging substrates become warped by film stress and thermal cycling, stressing already tight process windows.

## E. Lithographic Process

A battery of tests were done on 200mm Si wafers seeded with copper and then coated with the photoresist to a film thickness (FT) of  $50\mu$ m. The process was tested for the three different stepper configurations shown in Fig. 1.

| Lens NA | Wavelength |  |  |  |  |

|---------|------------|--|--|--|--|

| 0.1     | ghi-line   |  |  |  |  |

|         | i-line     |  |  |  |  |

| 0.145   | i-line     |  |  |  |  |

|         |            |  |  |  |  |

Fig. 1: Stepper configurations tested

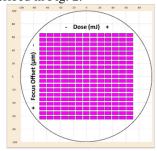

The first step was to expose an E0/dose-to-clear (DTC) array. A DTC array contains an array of open field exposures that increment upward in exposure energy. After development, the DTC is determined by the finding the first completely clear cell on the array and then identifying its dose. Using the DTC as the starting dose and incrementing by 0.15 of the DTC at each step, a focus exposure matrix (FEM) was exposed. A FEM wafer layout allows for quick and efficient characterization of the lithographic process window and the focus and exposure settings needed to achieve the best result. The matrix is described in Fig. 2.

Fig. 2: Focus exposure matrix wafer layout

The FEM results were plotted into latitude curves which helped identify the process window for each particular lithographic condition. Fig. 3 shows exposure latitude and focus latitude for  $25\mu$ m VIA's in the different configurations.

Fig. 3: (a) Exposure Latitude, (b) Focus Latitude for  $25\mu m$  VIA's

Using the exposure and focus parameters found in the last step, wafers were exposed using the custom reticle manufactured for this study. After exposure, the wafers were plated and the resist stripped.

# **III. Results and Discussion**

#### A. Lithographic Results

Fig. 4 tabulates all of the data gleaned from the initial targeting phase. In all cases, the stepper and resist combination yield over 40% exposure latitude coupled with

upwards of  $85\mu$ m depth of focus. These are all attributes that are conducive to and required for a large process window which in turn leads to larger yields.

|                          |          | 0.10 NA |       | 0.10 NA |       |       | 0.145 NA |       |       |

|--------------------------|----------|---------|-------|---------|-------|-------|----------|-------|-------|

|                          | ghi-line |         |       | i-line  |       |       | i-line   |       |       |

|                          | 15 μm    | 20 µm   | 25 µm | 15 μm   | 20 µm | 25 µm | 15 μm    | 20 µm | 25 µm |

| Eo (mJ/cm <sup>2)</sup>  | 240      |         |       | 110     |       |       | 105      |       |       |

| Eop (mJ/cm <sup>2)</sup> | 578      | 586     | 597   | 263     | 254   | 263   | 223      | 216   | 210   |

| Exposure<br>Latitude (%) | >43      | >51     | >54   | >57     | >63   | >63   | 50       | >57   | >59   |

| Focus<br>Latitude (µm)   | >90      | >90     | >90   | >90     | >90   | >90   | >85      | >90   | >90   |

| Resolution<br>(µm)       | 5        |         |       | 5       |       |       | 5        |       |       |

Fig. 4: Overview of lithographic data

A sampling of the resultant vias from the 0.1NA ghi-line lithography step pre-plating are shown in Fig. 5. Because these vias are the effective mold for the plating step, it is critical that the profile is optimized. The profile of the final via appears to be dependent on the exposure dose.

**Fig. 5:** SEM micrograph of vias exposed using 0.1NA lens at ghi-line in 50μm of INTERVIA<sup>TM</sup> BCPR-i 4500 Photoresist

#### B. Lithography Impact on Copper Pillar Profile

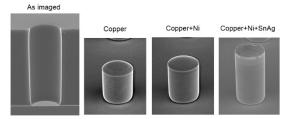

The final copper pillars exhibit excellent conformity to the photoresist via molds created during the exposure and develop process. Fig. 6 shows the progression of the copper pillar form through the entire process. The profiles correlate with what was observed in the photoresist SEM cross sections. Sidewall angles of roughly 90 degrees are demonstrated along with a smooth defect-free top.

**Fig. 6:** SEM micrograph of  $15\mu$ m copper pillar showing same base profile as photoresist images

#### C. Importance of CD Control on Copper Pillar Height

For advanced packaging applications, precise copper pillar height control is essential, and lithography CD control plays an important part in the plating process since CD variation directly affects plated height. The electroplating rate is proportional to current per unit area, i.e. the open area at the bottom of the photoresist openings at the beginning of the process, and the area of the evolving metal surface during deposition. Variation in CD or sidewall angle across the wafer will result in a corresponding change in copper pillar height. For example, in the case of copper pillar features a 5% change in CD can cause a 10% change in plated height.

#### D. Ultimate Pitch

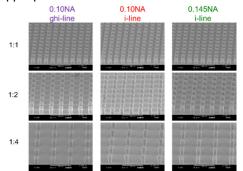

The well-sculpted sidewalls of the exposed via molds and the subsequently plated copper pillars with no foot are exactly the traits needed in order to push the boundaries on pillar densities. Fig. 7 illustrates the final plating results of  $15\mu m$  copper pillars.

Fig. 7: 15µm copper pillars at various densities

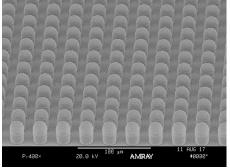

The final performance achieved was  $15\mu m$  copper pillars plated to a height of  $36\mu m$  at a pillar pitch of 1:1 (Fig. 8).

Fig. 8: 15µm copper pillars plated to 39µm at 1:1 pitch

The reticle used for the FEM characterizations included features that were smaller than those available on the custom plating reticle and demonstrated that there is performance down to  $5\mu$ m (Fig. 9). That is proven efficacy of the creation of vias with up to 10:1 aspect ratio using all three lens/wavelength combinations.

**Fig. 9:** 5µm vias in 50µm of the **p**hotoresist demonstrated using all three configurations.

## **IV. Conclusion**

The results of this study demonstrate that it is physically possible to fabricate copper pillars of more than  $35\mu$ m in height, with aspect ratio up to 2:1 through the use of advanced packaging stepper lithography in chemicallyamplified resist in conjunction with electroplating systems. It is clear that maintaining good CD control, throughout the entire photoresist profile, is essential to achieving consistent copper pillar height which directly impacts the yield and reliability of the final package. Lastly, contrary to conventional wisdom, high NA (>0.15) is not always better. Low NA lenses will be necessary for their large DOF to properly image VIA molds required in the continued evolution of 3D packaging.

## Acknowledgment

The authors wish to thank Corey Shay (Rudolph Technologies) for generating the lithography structures required for the electroplating process and the photoresist SEM micrographs for this paper. We would also like to thank Regina Cho and Lou Grippo (Dow Electronic Materials) for completing all of the electroplating work, and Melissa Nocchi and John Nelson (Dow Electronic Materials) for generating the SEM images for process window analysis.

#### References

- Clive Maxfield, EE Times Article, 4/8/2012: "2D vs. 2.5D vs. 3D ICs 101"

- [2] Toward 2.5/3D Packaging Enablement through Copper Pillar Technology Deborah S. Patterson Amkor Technology. Volume 16, Number 3 May - June 2012

- [3] Ron Huemoeller, AMKOR Technology, Architectural Success of 2.1D & 2.5D, SEMI 3D Summit, Grenoble, France, January 2014

- [4] Tom Strothman, STATSChipPac, Encapsulated Wafer Level Package Technology (eWLCS), ECTC 2014, Orlando, FL.